# PA-2000

# MAIN BOARD User's Guide

DOC No. : 14259

Revision : A0

Date : Apr. 1995

## HANDLING PRECAUTIONS

Static electricity may cause damage to the integrated circuits on the mainboard. Before handling any mainboard outside of its protective packaging, ensure that there is no static electric charge in your body.

Danger of explosion if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

Observe any or all of these basic precautions when handling the mainboard or other computer components:

- Wear a static wrist strap which fits around your wrist and is connected to a natural earth ground.

- Touch a grounded or anti-static surface or a metal fixture such as a water pipe.

- Avoid contact with the components on add-on cards, boards and modules and with the "gold finger" connectors plugged into the expansion slot. It is best to handle system components by their mounting bracket.

Above methods either prevent static build-up or cause it to be discharged properly.

#### TRADEMARKS ™

IBM

registered trademark of International Business Machines Corp. registered trademark of Intel Corp.

Intel/ Pentium

All other trademarks mentioned in this manual are registered property of the respective owners.

#### **COPYRIGHT®**

This manual may not, in whole or in part, be photocopied, reproduced, transcribed, translated, or transmitted in whatsoever form without the written consent of the manufacturer, except for copies retained by the purchaser for personal archival purposes.

## **Table of Contents**

| Chap    | oter 1 Overview                                        |     |     | 7.10       |            |      |     | -  | 1/10 |      |        | _  |      |     | _                 | _ |

|---------|--------------------------------------------------------|-----|-----|------------|------------|------|-----|----|------|------|--------|----|------|-----|-------------------|---|

|         | Specifications  Mainboard Layout  System Block Diagram |     |     |            | d.         | à    |     | ٨  | ie   | ١.   |        | 'n |      |     | 1 -<br>1 -<br>1 - | • |

| -       | oter 2 Mainboard Settings                              | -   | -   | -          |            | -    | 111 | -  | 177  | 100  |        | -  |      |     |                   | 7 |

|         | Jumpers                                                |     |     | lin<br>est | riv<br>Liv | i in | ė,o |    |      |      |        |    | •    |     | 2 -<br>2 -        |   |

|         | Jumper Setting for I/O                                 |     |     |            | 10° 1      | 10   |     | i. |      | · in | ÷      |    |      |     | 2 -               |   |

|         | Jumper Setting for System                              |     |     |            |            |      |     |    |      |      |        |    |      |     | 2 -               |   |

| Cha     | oter 3 System Memory                                   | i v | -16 | 60/3       |            |      |     |    |      |      |        |    |      |     |                   |   |

| Tangara | Memory Locations                                       |     |     |            | 15.        |      | 1   |    | •    |      |        |    | -1   | 100 | 3 -               |   |

|         | Installing DRAM                                        |     |     |            |            |      | Ĭ,  |    |      |      |        |    |      |     | 3 -               |   |

|         | SIMM Banks                                             |     |     |            |            |      |     |    |      |      |        | ÷  |      |     | 3 -               |   |

|         | DRAM Configuration                                     |     |     |            |            |      | ÷   |    |      |      |        |    |      |     | 3 -               |   |

|         | Installation Instructions                              |     |     |            |            |      |     |    |      |      | i<br>i |    | de l |     | 3 -               | 4 |

|         | Cache Memory                                           |     |     |            |            |      |     |    |      | į.   |        |    | 7,8  | 10  | 3 -               |   |

|         | Installing Cache Memory                                | 177 |     |            |            |      |     |    |      |      |        |    | fer. | · · | 3 -               |   |

|         | Cache SRAM Specifications an                           |     |     |            |            |      |     |    |      |      |        |    |      |     |                   |   |

|         | Using Various Voltage SRAM                             |     |     |            |            |      |     |    |      |      |        |    |      |     |                   |   |

|         | 256KB Cache SRAM                                       |     |     |            |            |      |     |    |      |      |        |    |      |     |                   |   |

|         | 512KB Cache SRAM                                       |     |     |            |            |      |     |    |      |      |        |    |      |     |                   |   |

|         | 1MB Cache SRAM                                         |     |     |            |            |      |     |    |      |      |        |    |      |     |                   |   |

| Cha     | pter 4 Award BIOS Setup                                |     |     |            |            |      |     |    |      |      |        |    |      |     |                   |   |

|         | CMOS Setup Litility                                    |     |     |            |            |      |     |    |      |      |        |    |      |     | 4 -               |   |

| Standard CMOS Setup .   |     |    |     | 1  | •   |   |   |     |   |    |     |   |   |     |   |     | 4-2    |

|-------------------------|-----|----|-----|----|-----|---|---|-----|---|----|-----|---|---|-----|---|-----|--------|

| BIOS Features Setup     |     |    |     |    |     |   |   |     |   |    |     |   |   |     |   | h.P | 4 - 4  |

| Chipset Features Setup  |     |    |     |    |     |   |   |     |   |    |     | , |   |     |   |     | 4 - 7  |

| Power Management Setup  |     |    |     |    |     |   |   |     |   |    |     |   |   |     |   |     | 4 - 11 |

| PCI Configuration Setup |     |    |     |    |     |   |   |     |   |    |     |   |   |     |   |     | 4 - 13 |

| Interrupt Assigments of | P   | CI | S   | lo | ts  |   |   |     |   |    |     |   | • |     |   | 4   | 4 - 15 |

| Load BIOS Defaults      |     |    |     |    | į.  |   | Ţ | II. |   |    |     |   |   |     |   | 4   | 4 - 16 |

| Load Setup Defaults     | e i |    |     |    |     |   |   |     |   |    | l.  |   |   |     |   | 4   | 4 - 16 |

| Supervisor/User Passwor |     |    |     |    |     |   |   |     |   |    |     |   |   |     |   | -   | 4 - 16 |

| Clear Password          |     |    |     |    |     |   |   |     | 1 |    |     |   |   |     |   | 4   | 4 - 17 |

| IDE HDD Auto Detection  | es  |    | io. | 9  |     |   | 9 | ¥.  | 1 | 90 |     |   | · | 13  | 0 | 4   | 4 - 17 |

| Save and Exit Setup     |     |    |     |    |     | 0 |   | 10  | 0 |    |     | 9 | 7 | 180 | 4 |     | 4 - 18 |

| Exit Without Saving     |     |    |     |    | 770 |   | 8 | 10  |   | 91 | 100 |   | 2 | 155 |   | d,  | 4 - 18 |

## **ABOUT THIS MANUAL**

This manual is designed to guide you and facilitate your use of the PA-2000 mainboard. It is divided into chapters. The chapters contain the main body of information normally referred to by users.

- **Chapter 1** gives an overview and introduces the basic parts and features of the mainboard.

- **Chapter 2** gives information on the jumper and connector settings on the mainboard.

- **Chapter 3** provides information on the memory subsystem of the mainboard in the form of SIMMs and Cache memory and describes how you can upgrade memory.

- Chapter 4 briefly explains the mainboard's BIOS system Setup in general and tells you how to run it and change the system configuration settings.

NOTE: The material in this manual is for information only and is subject to change without notice. We reserve the right to make changes in the product design without reservation and without notification to its users. We shall not be liable for technical or editorial omissions made herein; nor for incidental or consequential damages resulting from the furnishing, performance, or use of this material.

## ABOUT THIS MANUAL

the manual is designed to guided by writtent facts little bloom use or c PA 2000 mainly and It jackindos, etc. characters that characters contain the main of the factor and compathy referred to trusts.

to sound has a required and someound has well-revent about g

distributed.

distributed.

distributed.

distributed to the national college value of the main.

distributed to the national college value of the main.

beard in the form of SHAMs and Cache is onory as Laborabes have on our me ade memory.

briefly explains the realthole of a BIOS systems being a general and tells you have to run it use course the system our generalize

NOTE: The material in the manual is for intermation only and is subject to change without notice. We reserve the right to make changes in the product design without reservation and without notification is its users. We shall not be limble for teleknical or notification of the conscious made herein nor for motivated or gain, equential consequences are under the fundaments of the consequences of the formance, by use of the materials.

## Overview

The unsurpassed capabilities of the P54C 3.3V CPU combined with Intel's PCI Bus and the advanced features of VIA's VT82C570MV™ chipset make the PA-2000 mainboard the most powerful platform around. The incorporated enhanced PCI IDE support allows the installation of four host interface devices including a CD-ROM drive or a tape streamer. The two serial/one parallel I/O controller and PCI IDE controller chips are onboard to provide you more convenient connection choices for various peripheral devices. The mainboard supports an optional EDO (Extended Data Output) page mode DRAM function pushing overall mainboard performance to a new level.

This chapter gives you a brief overview of this mainboard, providing basic information on its major parts and components.

## **Specifications**

The PA-2000 mainboard comes with the following features:

- Intel P54C 3.3V CPU in a 320-pin ZIF socket.

- VIA VT82C570MVchipset for high performance.

- Supports 256KB/512KB standard 3.3V or mix voltage SRAM direct-mapped write-back cache memory.

- Supports 8 up to 192MB RAM in three banks using 72-pin SIMMs; provides standard or EDO page mode DRAM operation.

- Shadowing of system and Video BIOS to speed up access.

- Award BIOS.

- Supports 128KB Flash ROM.

- Built-in VIA 82C416MV<sup>TM</sup> provides internal keyboard controller, real-time clock and clock generator.

- Four 16-bit ISA expansion slot and three 32-bit PCI Bus master slots.

- Onboard NS 332/334TM I/O chipset supports two serial ports, one parallel port and FDC.

NOTE : When plugging your processor into the CPU (ZIF) socket, make sure that the pin 1 matches that of the CPU

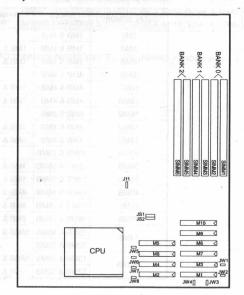

**Mainboard Layout**

PS/2 Mouse PS/2 Keyboard Connector Connector CN2 CN1 CN4 CN3 SL 87332 CN6 Power PCI2 82C576\_3V SL6 SL7 JP1 HDD\_LED Connector SIMM2 SIMM3 SIMM4 Green Status LED Connector VT82C 416MV 82C575MV\_3V CPU Fan Connector JC3 CN13 P54C Power LED and Keylock Connector

## **Mainboard Settings**

The PA-2000 has several user-adjustable jumpers on the board that allow you to configure your system to suit your every need. This chapter contains information on the various jumper settings on your mainboard.

## **Jumpers**

Jumpers are used to select the operation modes for your system. Some jumpers on the board have three metal pins with each pin representing a different function. To "set" a jumper, a black cap containing metal contacts is placed over the jumper pin/s according to the required configuration. A jumper is said to be "shorted" when the black cap has been placed on one or two of its pins, as shown in the figure below:

NOTE: Users are not encouraged to change the jumper settings not listed in this manual. Changing the jumper settings improperly may adversely affect system performance.

## Jumper Setting for CPU Clock

| CPU     | External | ONL   | 1140  |       | CPU C         | lock Ra | ate   |

|---------|----------|-------|-------|-------|---------------|---------|-------|

| Speed   | Clock    | JK1   | JK2   | JK3   | Int. Multiple | JC2     | JC3   |

| 133 MHz | 66 MHz   | 321   | 321   | 3 2 1 | 2 x Ext.      | 3 2 1   | 3 2 1 |

| 120 MHz | 60 MHz   | 3 2 1 | 321   | 3 2 1 | 2 x Ext.      | 3 2 1   | 3 2 1 |

| 100 MHz | 66 MHz   | 3 2 1 | 321   | 3 2 1 | 1.5 x Ext.    | 3 2 1   | 3 2 1 |

| 90 MHz  | 60 MHz   | 3 2 1 | 3 2 1 | 3 2 1 | 1.5 x Ext.    | 3 2 1   | 3.2.1 |

| 75 MHz  | 50 MHz   | 3 2 1 | 3 2 1 | 3 2 1 | 1.5 x Ext.    | 3 2 1   | 3 2 1 |

| Bus / CPU Clock Ratio         | JC2   | JC3   |

|-------------------------------|-------|-------|

| could a requ2:3 "test of and  | 3.2.1 | 321   |

| 1.2                           | 3 2 1 | 3.2.1 |

| no soo, no bijo 3; need and g | 3.2.1 | 3.2.1 |

| 2:5                           | 3 2 1 | 3 2 1 |

## Jumper Setting for I/O

| J1    | rit apr | Display Type                   |

|-------|---------|--------------------------------|

| muj j |         | Mono/EGA/VGA                   |

| ohea  | -       | CGA Visitavis visit vise       |

| JCP   |         | Password Clear                 |

|       | **      | Enabled                        |

| 12    |         | Disabled (Default)             |

| JI    |         | NS87332/87334                  |

|       |         | IR serial port (for NS334)     |

|       |         | COM Port (for NS332) (Default) |

## **Jumper Setting for System**

|     |        | CPU   | /oltage                    |

|-----|--------|-------|----------------------------|

|     | Others | 3.3 V | 3.5 V (Default)            |

| J15 |        |       | and iniq-10 ments nearly a |

| J16 |        |       | •••                        |

|    | September 1 | and the same of |                                             |

|----|-------------|-----------------|---------------------------------------------|

| JO | 01          | 111.00          | Internal Write-Back/<br>Write-Through Cache |

| +. | 1           | 3 2 1           | Write-Back (Default)                        |

|    |             | 3 2 1           | Write-Through                               |

| JF | 2           |                 | Hardware Reset                              |

|    |             | -               | Enabled                                     |

|    |             |                 | Disabled (Default)                          |

| J1 | 7           |                 | Programmable Flash<br>EPROM Type            |

|    |             | 2 : 3           | Intel 28F001BX-T                            |

|    |             | 1 2 3 1         | SST 29EE010 (Default)                       |

## Connector Pin Definitions

| Connector                      | Pin No. | Definitons |

|--------------------------------|---------|------------|

| J9                             | 100 100 | +5V        |

| (Green Power Supply Connector) | 2       | GND        |

This connector is a green power 2-pin disable outlet connector. When the system enter the suspend mode, the monitor will be left blank.

| Connector           | Pin No.              | Definitons |

|---------------------|----------------------|------------|

| J13 PROSS YOU       | nert experience in a | GND        |

| (CPU Fan Connector) | 2                    | +12V       |

|                     | 3                    | GND        |

Chapter 3

## **System Memory**

The PA-2000 can be equipped with the necessary memory for running all your applications. Memory comes in the form of DRAM (SIMMs) and cache SRAM. This chapter describes these two types of memory and gives instructions on how to install each type on the mainboard.

## **Memory Locations**

The board layout below shows the locations of the DRAM memory banks and the cache SRAM:

System Memory

3 - 3

## **Installing DRAM**

## **SIMM Banks**

The PA-2000 can accommodate onboard memory from 2 to 192MB using SIMMs (Single-In-Line Memory Modules). The mainboard has three memory banks — Bank 0, Bank 1, and Bank 2. Each bank has two SIMM sockets which can accept either a 1MB, 4MB, 8MB, 16MB or 32MB SIMM in each socket.

## **DRAM Configuration**

Memory can be installed in a variety of configurations, as shown in the following table:

| TOTAL MEMORY | BANK 0<br>(72-PIN x 2) | BANK 1<br>(72-PIN x 2) | BANK 2<br>(72-PIN x 2) |

|--------------|------------------------|------------------------|------------------------|

| 2MB          | 1MB & 1MB              |                        |                        |

| · 4MB        | 1MB & 1MB              | 1MB & 1MB              |                        |

| 6MB          | 1MB & 1MB              | 1MB & 1MB              | 1MB & 1ME              |

| 8MB          | 4MB & 4MB              |                        |                        |

| 10MB         | 4MB & 4MB              | 1MB & 1MB              |                        |

| 12MB         | 4MB & 4MB              | 1MB & 1MB              | 1MB & 1MB              |

| 16MB         | 8MB & 8MB              |                        |                        |

| 18MB         | 8MB & 8MB              | 1MB & 1MB              |                        |

| 24MB         | 4MB & 4MB              | 4MB & 4MB              | 4MB & 4MB              |

| 32MB         | 16MB & 16MB            |                        |                        |

| 34MB         | 16MB & 16MB            | 1MB & 1MB              |                        |

| 36MB         | 16MB & 16MB            | 1MB & 1MB              | 1MB & 1MB              |

| 40MB         | 16MB & 16MB            | 4MB & 4MB              |                        |

| 42MB         | 16MB & 16MB            | 4MB & 4MB              | 1MB & 1MB              |

| 48MB         | 16MB & 16MB            | 8MB & 8MB              |                        |

| 64MB         | 16MB & 16MB            | 16MB & 16MB            | *                      |

| OHIVID       | 32MB & 32MB            |                        |                        |

| 66MB         | 16MB & 16MB            | 16MB & 16MB            | 1MB & 1MB              |

| OOIVID       | 32MB & 32MB            | 1MB & 1MB              |                        |

TOTAL MEMORY 1MB & 1MB 32MB & 32MB 1MB & 1MB 68MB **4MB & 4MB** 16MB & 16MB 16MB & 16MB **72MB** 32MB & 32MB 4MB & 4MB 32MB & 32MB 4MB & 4MB 1MB & 1MB **74MB** 4MB & 4MB **4MB & 4MB** 80MB 32MB & 32MB 16MB & 16MB 16MB & 16MB 16MB & 16MB 96MB 16MB & 16MB 32MB & 32MB 32MB & 32MB | 16MB & 16MB 1MB & 1MB **98MB 4MB & 4MB** 32MB & 32MB 16MB & 16MB 104MB 16MB & 16MB 16MB & 16MB 32MB & 32MB 128MB 32MB & 32MB 32MB & 32MB 32MB & 32MB | 32MB & 32MB 1MB & 1MB 130MB 32MB & 32MB | 32MB & 32MB **4MB & 4MB** 136MB 32MB & 32MB | 32MB & 32MB | 16MB & 16MB 160MB

32MB & 32MB | 32MB & 32MB | 32MB & 32MB

NOTE: All memory banks use 72-pin memory modules.

192MB

## **Installation Instructions**

NOTE: Always observe static electricity precautions. See "Handling Precautions" at the start of this manual.

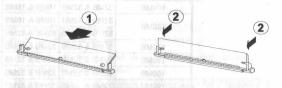

- 1. Locate the SIMM banks on the mainboard.

- Insert the SIMM edge connector at a 90-degree angle onto the socket.

Carefully push the SIMM down and back into the socket until the retaining clips of the socket snap, holding the SIMM in place. The holes in the SIMM should match the pins on the socket's retaining clips.

To remove the SIMM/s, pull the retaining latch on both ends of the socket and reverse the procedure above.

## **Cache Memory**

The PA-2000 can accept standard 3.3V or mix voltage cache SRAM of 256/512KB in DIP packages. Every time the CPU wants to write data to the external memory, if the location in SRAM is a "hit", it writes this data to the cache RAM directly, not to the DRAM.

NOTE: Use the correct chips for the amount of cache memory you want to add. Install both the correct Cache and Tag SRAM. Alter RAM type is the same as Tag RAM.

## **Installing Cache Memory**

NOTE: Always observe static electricity precautions. See "Handling Precautions" at the start of this manual.

If you do not have the confidence to make the installation, better consult a service technician for assistance.

- 1. Locate the cache memory on the mainboard.

- 2. Be guided by the Cache SRAM settings depending on your desired SRAM configuration.

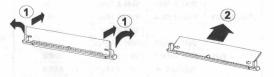

Correct orientation of the chip is necessary for the cache to operate properly. Normally, the chips have either a curved notch or a dot. This marker on the chip must be matched to the marker on the socket for correct alignment.

Install the chips individually as follows:

- Align the chip with the marker on the socket. Press the chip onto the socket, ensuring that the pins on the chip are aligned with the corresponding connections on the socket.

- Press the chip completely into the socket so that the pins are properly seated.

## **Cache SRAM Specifications and Settings**

## **Using Various Voltage SRAM**

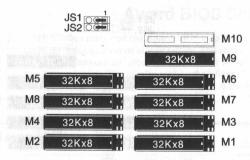

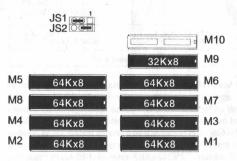

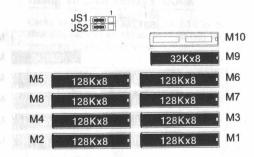

Cache sockets M1 to M8 can take 3.3V or mix-voltage SRAMs. However, cache socket M9 and M10 can only take 5.0V SRAMs. The jumper settings are listed below.

| lumper setti<br>nix-voltage | SRAMs (M1-M8).             |

|-----------------------------|----------------------------|

| • • JW5                     | JW1                        |

| •• JW6                      | JW2                        |

| • • JW7                     | JW4 JW3                    |

| •• JW8                      | no. I tran I to not vez ti |

| Jumper setti                |                            |

| 3.3V SRAMs                  | (M1-M8).                   |

|                             | (M1-M8).                   |

| 3.3V SRAMs                  | confident or one made in   |

| 3.3V SRAMs                  | . JW1                      |

#### 256KB Cache SRAM

#### 512KB Cache SRAM

#### **1MB Cache SRAM**

Chapter 4

## **Award BIOS Setup**

The PA-2000 comes with the Award BIOS chip that contains the ROM Setup information of your system. This chip serves as an interface between the processor and the rest of the main-board's components. This chapter explains the information contained in the Setup program and tells you how to modify the settings according to your system configuration.

## **CMOS Setup Utility**

| CMOS S                                                                                                                                               | A BIOS (2A5L7F09)<br>ETUP UTILITY<br>OFTWARE, INC.                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| STANDARD CMOS SETUP BIOS FEATURES SETUP CHIPSET FEATURES SETUP POWER MANAGEMENT SETUP PCI CONFIGURATION SETUP LOAD BIOS DEFAULTS LOAD SETUP DEFAULTS | SUPERVISOR PASSWORD<br>USER PASSWORD<br>IDE HDD AUTO DETECTION<br>SAVE & EXIT SETUP<br>EXIT WITHOUT SAVING |

| ESC : Quit<br>F10 : Save & Exit Setup                                                                                                                | ↑ ↓ → ← : Select Item<br>(Shift) F2 : Change Color                                                         |

A Setup program, built into the system BIOS, is stored in the CMOS RAM. This Setup utility program allows changes to the mainboard configuration settings. It is executed when the user changes system configuration; the user changes system backup battery; or the system detects a configuration error and asks the user to run the Setup program. As power-on RAM testing, the message "Press DEL to enter Setup (JCP)." appears. Use the arrow keys to select and press <Enter> to run the selected program.

Award BIOS Setup

## **BIOS Features Setup**

| BIO                                                                                                                                                                                                                          | CI/ISA BIOS (2A5L7F0H)<br>S FEATURES SETUP<br>RD SOFTWARE, INC. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Virus Warning Distremal Cache External Cache Distremal Cache | Disabled   C8000 - CBFFF   Disabled                             |

| Typematic Rate Setting Disabled Typematic Rate (Chars/Sec): 6 Typematic Delay (Msec) : 250 Security Option Setup PS/2 mouse function control: Disabled                                                                       | ESC : Quit                                                      |

#### **Virus Warning**

When enabled, assigns the BIOS to monitor the master boot sector and the DOS boot sector of the hard disks.

The options are: Enabled, Disabled (Default)

#### **External Cache**

Supports an optional cache SRAM.

The available options are: Enabled (Default), Disabled.

#### **Quick Power On Self Test**

Allows the BIOS to bypass the extensive memory test.

The options are: Enabled, Disabled (Default).

#### **Boot Sequence**

Allows the system BIOS to first try to boot the operating system from the first hard disk drive, drive C:.

The options are: A, C (Default); C, A.

#### **Swap Floppy Drive**

Allows you to switch the order in which the system accesses the floppy drives.

The options are: Enabled, Disabled (Default).

#### **Boot Up Floppy Seek**

Assigns the BIOS to perform floppy disk drive tests by issuing the time-consuming seek commands.

The options are: Enabled (Default), Disabled.

#### **Boot Up Numlock Status**

Allows the BIOS to automatically enable the Num Lock function when the system boots.

The options are: On (Default), Off.

#### Port 92H Fast A20G

When enabled, allows the A20G bus line signal generated from the chipset VT82C575MV PC/AT to directly pass to port 92H, instead of the keyboard controller. It will speed up the system performance.

The options are: Fast (Default),

#### **Memory Parity Check**

Allows the DRAM to execute parity bit check.

The options are: Disabled (Default), Enabled.

#### **Typematic Rate Setting**

Allows you to change the typematic repeat rate.

The options are: Disabled (Default), Enabled.

#### Typematic Rate (Chars/Sec)

The rate that the keyboard keys repeat the character when the key is held down.

The options are: 6 (Default), 8, 10, 12, 15, 20, 24, 30.

#### Typematic Delay (Msec)

The keyboard keys are "typematic," means that when a keyboard key is held down, the character repeats until the key is released. You can select a delay time before the character repeats.

The options are: 250 (Default), 500, 750, 1000 millisecond.

#### **Security Option**

Allows you to set the security level when booting up the system.

The available options are: Setup (Default), System.

#### PS/2 mouse function control

When enabled, allows you to release IRQ 12 for using the PS/2 mouse.

The options are: Enabled, Disabled (Default)

#### **Video BIOS Shadow**

Allows the BIOS to copy the video ROM code of the add-on video card to system memory for faster access.

The options are: Enabled (Default), Disabled.

#### C8000-CBFFF to DC000-DFFFF Shadow

Allows the BIOS to copy the BIOS ROM code of the add-on card to system memory for faster access. It may improve the performance of the add-on card.

Some add-on cards will not function properly if its BIOS ROM code is shadowed. To use these options correctly, you need to know the memory address range used by the BIOS ROM of each add-on card.

The available options are: Enabled, Disabled (Default).

### **Chipset Features Setup**

|                                                                                                       | CMOS SETU<br>CHIPSET FEAT                        |                                                                                                                        |                                                                   |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Decoupled Refresh<br>Video BIOS Cacheable<br>System BIOS Cacheable                                    | : Enabled<br>: Enabled<br>: Enabled              | DRAM for BANK 0<br>DRAM for BANK 1<br>DRAM for BANK 2                                                                  | : Standard<br>: Standard<br>: Standard                            |

| Memory Hole At 15Mb Addr.<br>Cache Timing Control<br>DRAM Timing Copntrol<br>SRAM Tag/Alt Bit Config. | : Disabled<br>: Fast<br>: Fast<br>: 7 Tags + ALT | Onboard IDE 2nd Port<br>Onboard FDC Control<br>Onboard Serial Port 1<br>Onboard Serial Port 2<br>Onboard Parallel Port | : Enable<br>: Enable<br>: COM1/3F8H<br>: COM2/2F8H<br>: 378H/IRQ7 |

| Onchip IDE first channel IDE HDD Block Mode IDE Primary Master PIO                                    | : Enabled<br>: Enabled<br>: Auto                 | Onboard Printer Mode<br>ECP Use DMA Channel N                                                                          | : Compatible                                                      |

| IDE Primary Slave PIO                                                                                 | ; Auto                                           |                                                                                                                        | 0/+/- : Modify<br>F2 : Color                                      |

#### **Decoupled Refresh**

The onboard DRAM can be decoupled from ISA bus memory device so that the processor can re-access the onboard DRAM without waiting for the completion of ISA bus memory refresh.

Disabled it if you use ISA type ET-4000 VGA card.

The available options are: Enabled (Default), Disabled.

#### Video BIOS Cacheable

Allows the system to use the video BIOS code from the cache instead of the slower DRAMs or ROMs.

The available options are: Enabled (Default), Disabled.

#### System BIOS Cacheable

Allows the ROM area F000H-FFFFH cacheable as cache controller is enabled.

The available options are: Enabled (Default), Disabled.

#### Memory Hole At 15MB Addr.

When enabled, every time the processor accesses the 15~16MB address, memory hole at the 15MB address will be relocated to the 15~16MB address range of the ISA cycle. When disabled, it will let the memory hole at the 15MB address decode be treated as a DRAM cycle when processor accesses the 15~16MB address.

The available options are: Enabled, Disabled (Default).

#### Cache Timing Control

Allows you to adjust the access speed of VT82C575MV to external cache.

The options are: Normal, Fast, Turbo (Default).

#### **DRAM Timing Control**

Allows you to speed up the data access of VT82C575MV.

The options are: Normal, Fast (Default).

### SRAM Tag/Alt Bit Config.

Allows the alter bit to check whether or not the external cache writes back data to main memory.

The options are: 7Tags+ALT (Default), 10Tags+ALT, 8 Tags.

#### Onchip IDE first channel

When enabled, allows the IDE drive to use the PCI IDE first channel.

The options are: Enabled (Default), Disabled.

#### **IDE HDD Block Mode**

Allows the system to execute read/write requests to hard disk in block mode.

The options are: Enabled (Default), Disabled.

#### **IDE Primary Master PIO**

Allows you to select first PCI IDE channel of the primary master hard disk mode or to detect it by the BIOS.

The available options are: Auto (Default), Mode 0, Mode 1, Mode 2, Mode 3, Mode 4.

#### **IDE Primary Slave PIO**

Allows you to select the first PCI IDE channel of the primary slave hard disk mode or to detect it by the BIOS.

The available options are: Auto (Default), Mode 0, Mode 1, Mode 2, Mode 3, Mode 4.

#### DRAM for BANK 0-2

Select "EDO" when you use EDO DRAMs.

The options are: Standard (Default), EDO.

#### Onboard IDE 2nd Port

Allows you to use onboard IDE controller.

The options are: Enabled (Default), Disabled.

#### **Onboard FDC Control**

Allows you to enable the floppy disk controller (FDC).

The options are: Enabled (Default), Disabled.

#### **Onboard Serial Port 1**

Enable it if serial port 1 uses the onboard I/O controller. If some I/O card to be installed, COM 3 and COM4 may be needed. Select COM 3 or COM 4 by this feature.

The options are: COM1/3F8H (Default), COM2/2F8H, COM3/3E8H, COM4/2E8H.

#### **Onboard Serial Port 2**

Enable it if serial port 2 uses the onboard I/O controller. If some I/O card to be installed, COM 3 and COM4 may be needed. Select COM 3 or COM 4 by this feature.

The options are: COM1/3F8H, COM2/2F8H (Default), COM3/3E8H, COM4/2E8H.

#### **Onboard Parallel Port**

Enable it if parallel port uses the onboard I/O controller.

The options are: Disabled, 278H/IRQ5, 3BCH/IRQ7, 378H/IRQ5, 378H/IRQ7 (Default).

#### **Onboard Printer Mode**

Allows you to connect with advanced printer I/O mode.

The options are: EPP, ECP, Standard (Default).

#### ECP Use DMA Channel No.

Allows you to adjust the DMA channel number 3 or 1 for the ECP mode of printer.

The options are: 1, 3 (Default).

## **Power Management Setup**

|                                                                                            | CMOS S                                                  | A BIOS (2A5L7F0H)<br>ETUP UTILITY<br>IAGEMENT SETUP                                                                                     |                                                                           |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Doze Timer<br>Suspend Timer<br>Suspend Mode<br>HDD Power Management<br>VGA Activity Wakeup | Disabled 2 min 8 min Enabled Disabled Disabled Disabled | IRQ3 Activity<br>IRQ4 Activity<br>IRQ5 Activity<br>IRQ7 Activity<br>IRQ8 Activity<br>IRQ10 Activity<br>IRQ11 Activity<br>IRQ12 Activity | Primary Primary Primary Primary Secondary Primary Primary Primary Primary |

|                                                                                            |                                                         | ESC: Quit<br>F1: Help<br>F5: Old Values<br>F6: Load BIOS I<br>F7: Load Setup                                                            |                                                                           |

#### **Power Management**

Allows you to use Power Management features.

The available options are: Enabled, Disabled (Default).

#### **Doze Timer**

Processor speed will slowdown and enter "Doze Mode" assuming there is no operation during the selected period. Normal processor speed is resumed by pressing any key.

The options are: 8 sec, 32 sec, 2 min (Default), 8 min, 16 min.

#### **Suspend Timer**

VGA display will blank out and enter "Suspend Mode" if there is no operation during the selected period.

The available options are: 2, 8 (Default), 16 and 32 min.

#### **Suspend Mode**

Disabled it to render the Suspend Timer inoperative.

The options are: Enabled (Default), Disabled.

## HDD Power Management

Allows the HDD spindle motor to turn off after a certain time period.

The options are: Disabled (Default), 20, 30, 45, 60 min.

#### VGA Activity Wakeup

Allows the Doze Timer to count when no activity is detected on the VGA display. If disable it, the Doze Timer counts immediately even VGA display still acts.

The available options are: Enabled, Disabled (Default).

#### **Video Off Method**

The option "V/H SYNC+Blank" allows the BIOS to blank off screen display by turning off the V-Sync and H-Sync signals sent from add-on VGA card. "DPMS Supported" allows the BIOS to blank off screen display by your add-on VGA card which supports DPMS (Display Power Management Signaling function.) "Blank Screen" allows the BIOS to blank off screen display by turning off the red-green-blue signals.

The options are: DPMS Support (Default), V/H SYNC+Blank, Blank Screen.

#### **IRQ#** Activity

When "Primary", if the BIOS detects no IRQ# activity during the time specified by the Sleep Mode timer, the processor will power down. If "Secondary", the processor will power down after any IRQ activity.

The options are: Primary, Secondary.

The default values of IRQ3, 4, 5, 7, 10, 11, 12 are: Primary.

The default value of IRQ8 is: Secondary.

## **PCI Configuration Setup**

| PCI CONFIG                                                                                                | A BIOS (2A5L7F0H)<br>BURATION SETUP<br>OFTWARE, INC.                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PnP BIOS Auto-Config : Enabled Slot 1 Using INT# : Auto Slot 2 Using INT# : Auto Slot 3 Using INT# : Auto | CPU to PCI Write Buffer PCI Master Write Buffer PCI Master Prefetch PCI Master Prefetch PCI Master Burst Read PCI Master Burst Write PCI Dynamic Decoding PCI Dynamic Bursting PCI Dynamic Bursting PCI Dynamic Bursting |

| PCI IRQ Activated By Level PCI IDE IRQ Map To Primary IDE INT# : A Secondary IDE INT# : B                 | PCI Byte Merge : Disabled Local Memory Detect Point : Fast PCI Burst : Disabled PCI Master 0 WS Write : Enabled                                                                                                          |

|                                                                                                           | ESC: Quit ↑↓ ← Select Item F1 : Help PU/PD/+/- Modify F5 : Old Values (Shift) F2 : Color F6 : Load BIOS Defaults F7 : Load Setup Defaults                                                                                |

#### **PnP BIOS Auto-Config**

When enabled, the available IRQs used on the ISA slots are configured automatically by the BIOS. The options are: Enabled, Disabled (Default).

#### Slot 1-3 Using INT#

Allows the BIOS to automatically detect which interrupt is used by the card in selected PCI slot. The options are: Auto (Default), A, B, C, D.

#### Available IRQ

Allows the BIOS to assign an available IRQ if the attached PCI device needs IRQ to access the mainboard. The options are: NA, 5, 7, 9, 10, 11.

#### **PCI IRQ Actived By**

If your IDE card is trigged by edge, set it at "Edge". The options are: Level (Default), Edge.

#### PCI IDE IRQ Map To

Set Auto to allow the system BIOS automatically detect which interrupt is used by the PCI master drive. The options are: PCI-AUTO (Default), PCI-SLOT1, PCI-SLOT2, PCI-SLOT3, PCI-SLOT4, ISA.

#### CPU to PCI Write Buffer

When enabled, allows data and address access to the internal buffer of 82C576MV so the processor can be released from waiting state. The options are: Enabled (Default), Disabled.

#### **PCI Master Write Buffer**

When enabled, allows PCI write operation by informing the CPU of pending data from the PCI device. The processor is released from the waiting state by a signal from the master card. The options are: Enabled (Default), Disabled.

#### **PCI Master Prefetch**

When enabled, allows the data and address to be saved in the internal buffer of 82C576MV to reduce the master drive access time. The options are: Enabled (Default), Disabled.

#### **PCI Master Burst Read**

When enabled, allows the PCI master drive to burst read data from the system, instead of the normal speed (32 bits at a time). It increases the data transfer from PCI to the system. The options are: Enabled (Default), Disabled.

#### **PCI Master Burst Write**

When enabled, allows the PCI master drive to burst write data to the system, instead of the normal speed (32 bits at a time). It increases the data transfer from PCI to the system. The options are: Enabled (Default), Disabled.

#### **PCI Dynamic Decoding**

When enabled, allows the PCI IDE controller to automatically decode the next 1KB codes that come after a PCI cycle. It will improve the system performance. The options are: Enabled (Default), Disabled.

#### **PCI Dynamic Bursting**

When enabled, allows the processor to execute the "Burst write" function during a PCI cycle. The options are: Enabled (Default), Disabled.

#### **PCI Byte Merge**

When enabled, allows the PCI cycle to send data out only after the internal buffer of 82C576MV is filled up completely. If you are using Trident 9440 PCI VGA card (VC-910), AVANCE ALG 2301 PCI VGA card or KELVIN 64-PCI (Cirrus 5434) PCI VGA card, keep this feature disabled. The options are: Disabled (Default), Enabled

#### **Local Memory Detect Point**

If set at Fast, the PCI access to the same 1KB address in memory will be reduced one PCI cycle. If you are using the Adaptec PCI SCSI Card AHA-2940/45, please set at "Medium". The options are: Fast (Default), Medium.

#### **PCI Burst**

When enabled, it will improve the data transfer on PCI Buses. Disable it during trouble-shooting. The options are: Disabled, Enabled (Default).

#### PCI Master 0 WS Write

When enabled, allows zero wait state cycle delay when the PCI master drive writes data to DRAM. The options are: Enabled (Default), Disabled.

## **Interrupt Assignments of PCI Slots**

| SLOT               | INT OF SLOT        | INT OF VT82C576 |

|--------------------|--------------------|-----------------|

|                    | A                  | A               |

| Setup A survey     | B B barried        | В               |

| s blod nedroth wir | med has pC at hear | C               |

| Someone at The ac- | _                  |                 |

| any to enter the C |                    | D               |

| B B                |                    | C .             |

|                    | C                  | D               |

|                    | D                  | A               |

| Danzator at sports |                    | C               |

| to a brown zari es | В                  | D               |

| names and easter o | C                  | A               |

|                    | D                  | B.              |

#### **Load BIOS Defaults**

BIOS defaults contain the most appropriate values of the system parameters that allow minimum configuration for a satisfactory system performance. The OEM manufacturer may change the defaults through MODBIN before the binary image burns into the ROM.

## **Load Setup Defaults**

Selecting this field loads the factory defaults for BIOS and Chipset Features which the system automatically detects.

## Supervisor/User Password

To enable the Supervisor/User passwords, select the item from the Standard CMOS Setup. You will be prompted to create your own password. Type your password up to eight characters and press <Enter>. You will be asked to confirm the password. Type the password again and press <Enter>. You may also press <Esc> to abort the selection and not enter a password. To disable password, press <Enter> when you are prompted to enter password. A message appears, confirming the password is disabled.

Under the BIOS Feature Setup (refer to page 4-4) if System is selected under the Security Option field and the Supervisor Password is enabled, you will be prompted for the Supervisor Password every time you try to enter the CMOS Setup Utility. If System is selected and the User Password is enabled, you will be requested to enter the User Password every time you reboot the system. If Setup is selected under the Security Option field and the User Password is enabled, you will be prompted only when you reboot the system.

#### **Clear Password**

If you forget your password, turn off the system power first and remove the system unit cover. Locate Jumper JCP and cap it. Remove Jumper JCP and reset the system. At this point, you will not be asked for the password to enter Setup.

#### **IDE HDD Auto Detection**

The IDE Hard Disk Drive Auto Detection BIOS feature automatically detects your new hard disk drive type. Use it for a quick configuration of new hard drives.

NOTE: After your new hard disk type has been automatically configured by the BIOS, avoid pressing "Esc" if you wish to quit this screen and skip back to the CMOS Setup Utility screen otherwise you may lose all the modified settings. Follow the screen instructions on how to return to the Setup Utility screen instead.

## Save and Exit Setup

ROM PCI/ISA BIOS (2A5L7F09) CMOS SETUP UTILITY AWARD SOFTWARE, INC.

STANDARD CMOS SETUP

BIOS FEATURES SETUP

CHIPSET FEATURES SETUP

POWER MANAGEMENT SETUP

PCI CONFIGURATION SETUP

LOAD BIOS SAVE to CMOS and EXIT (Y/N)? Y

LOAD SETUP DEFAULTS

SUPERVISOR PASSWORD IDE HDD AUTO DETECTION

ESC : Quit F10 : Save & Exit Setup

↑ ↓ → ← : Select Item (Shift) F2 : Change Color

SAVE DATA TO CMOS and EXIT SETUP

After you have made changes under Setup, press < Esc> to return to the main menu. Move cursor to "Save and Exit Setup" or press "F10" and then press "Y" to change the CMOS Setup. If you did not change anything, press <Esc> again or move cursor to "Exit Without Saving" and press "Y" to retain the Setup settings. As you select this feature, the following message will appear at the center of the screen to allow you to save data to CMOS and exit the setup utility.

SAVE to CMOS and EXIT (Y/N)?

## **Exit Without Saving**

As you select this feature, the following message will appear at the center of the screen to allow you to save data to CMOS and exit the setup utility.

Quit Without Saving (Y/N)?

NOTE: Default values of the various Setup items on this chapter may not necessarily be the same ones shown on your screen.

## Update Note

To : Users of PA-2000 Manual (Rev : A0) Date : Nov., 17, F, 1995

If your manual's released date is Sep. 1995 or later, please pay attention to the following:

| CPU Exter | External |             |            |               | CPU Clock Rate |              |

|-----------|----------|-------------|------------|---------------|----------------|--------------|

| Speed     | Clock    | ock JK1 JK2 | JK3        | Int. Multiple | JC2            |              |

| 133 MHz   | 66 MHz   | <b>=</b> 5  | <b>=</b> - | C (m)         | 2 x Ext.       | 0 🖦          |

| 120 MHz   | 60 MHz   | [ <b>**</b> | D <b>=</b> | O <b>P</b>    | 2 x Ext.       | o <b>=</b>   |

| 100 MHz   | 66 MHz   |             | <b></b> 0  |               | 1.5 x Ext.     | <b>=</b>     |

| 90 MHz    | 60 MHz   | O <b></b>   | 0          | O <b>S</b>    | 1.5 x Ext.     | <b>=</b> 0   |

| 75 MHz    | 50 MHz   | <b>.</b>    | 0          |               | 1.5 x Ext.     | <b>9=0</b> G |

25-10336-04