### 1 Overview

Vortex86SX is the x86 SoC (System on Chip) with 0.13 micron process and ultra low power consumption design (less than 1 watt). This comprehensive SoC has been integrated with rich features, such as various I/O (RS-232, Parallel, USB and GPIO), BIOS, WatchDog Timer, Power Management, MTBF counter, LoC (LAN on Chip),JTAG etc., into a 27x27 mm, 581-pin BGA packing single chip.

The Vortex86SX is compatible with Win CE, Linux and DOS. It integrates 32KB write through direct map L1 cache, 16-bit ISA bus, PCI Rev. 2.1 32-bit bus interface at 33 MHz, SDRAM, DDR2, ROM controller, IPC (Internal Peripheral Controllers with DMA and interrupt timer/counter included),

SPI (Serial Peripheral Interface), Fast Ethernet MAC, FIFO UART, USB2.0 Host and IDE controller into a System-on-Chip (SoC) design.

Furthermore, this outstanding Vortex86SX SoC can not only meet the requirements of embedded applications, such as Electronics Billboard, Firewall Router, Industrial Single-Board-Computers, Receipt Printer Controller, Thin Client PC, Auto Vehicle Locator, Finger Print Identification, Web Camera Thin Server, RS232-to-TCP Transmitter. but also can meet the critical temperature demand, spanning from -40 to +85  $^{\circ}$ C.

## 2 Features

#### ■ x86 Processor Core

6 stage pipe-line

#### ■ Embedded I/D Separated L1 Cache

16K I-Cache, 16K D-Cache

#### ■ SDRAM/DDRII Control Interface

- 16 bits data bus

- Support DLL for clock phase auto-adjustion

- SDRAM support up to 133MHz

- SDRAM support up to 128Mbytes

- DDRII support up to 166MHz

- DDRII support up to 256Mbytes

#### ■ IDE Controller

Support 2 channels Ultra-DMA 100 (Disk x 4)

#### ■ LPC (Low Pin Count) Bus Interface

- Support 2 programable registers to decode LPC address

- MAC Controller x 1

#### ■ PCI Control Interface

- Up to 3 sets PCI master device

- 3.3V I/O

### ■ ISA Bus Interface

- AT clock programmable

- 8/16 Bit ISA device with Zero-Wait-State

- Generate refresh signals to ISA interface during DRAM refresh cycle

- DMA Controller

- Interrupt Controller

### ■ Counter/Timers

- 2 sets of 8254 timer controller

- Timer output is 5V tolerance I/O on 2<sup>nd</sup> Timer

#### ■ MTBF Counter

#### Real Time Clock

Below 2uA power comsuption on Internal Mode (Estimation Value)

### **■** FIFO UART Port x 5 (5 sets COM Port)

- Compatible with 16C550/16C552

- Default internal pull-up

- Supports the programmable baud rate generator with the data rate from 50 to 460.8K bps

- The character options are programmable for 1 start bits; 1, 1.5 or 2 stop bits; even, odd or no parity; 5~8 data bits

- Support TXD\_En Signal on COM1/COM2

- Port 80h output data could be sent to COM1 by software programming

### ■ Parallel Port x 1

Support SPP/EPP/ECP mode

#### ■ General Chip Selector

- 2 sets extended Chip Selector

- I/O-map or Memory-map could be configurable

- I/O Addressing: From 2 byte to 64K byte

- Memory Address: From 512 byte to 4G Byte

### ■ General Programmable I/O

- Supports 40 dedicated programmable I/O pins

- Each GPIO pin can be individually configured to be

an input/output pin

### ■ USB 2.0 Host Support

- Supports HS, FS and LS

- 4 port

### ■ PS/2 Keyboard and Mouse Interface Support

- Compatible with 8042 controller

- Redundant System Support

- Speaker out

- Embedded 256KB Flash

- For BIOS storage

- The Flash could be disable & use external Flash ROM

- JTAG Interface supported for S.W. debugging

### ■ Input clock

- 14.318MHz

- 32.768KHz

### ■ Output clock

- 24 MHz

- 25 MHz

### Operating Voltage Range

- Core voltage: 1.30 V ~ 1.40V

- I/O voltage: 1.8V  $\pm$  5% , 3.3 V  $\pm$  10 %

### ■ Temperature

- Operating Temperature -40° ~ 85°

- Storage Temperature -50°C ~ 125°C

### ■ Package Type

27x27, 581 ball BGA

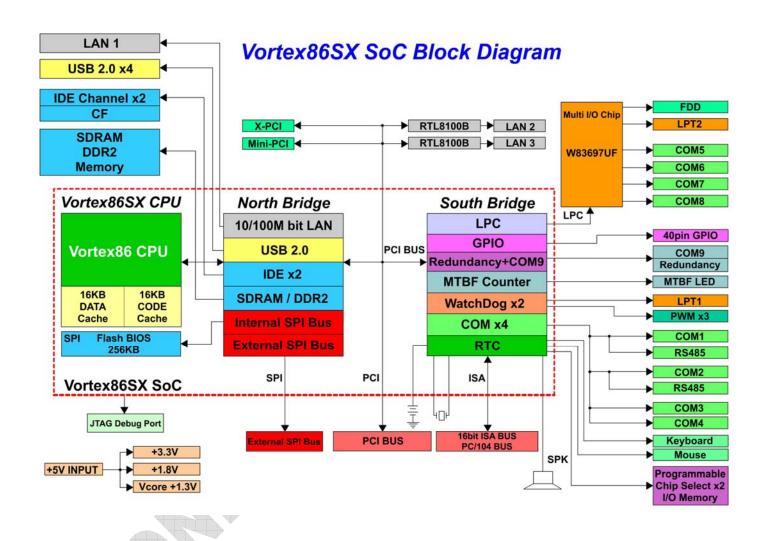

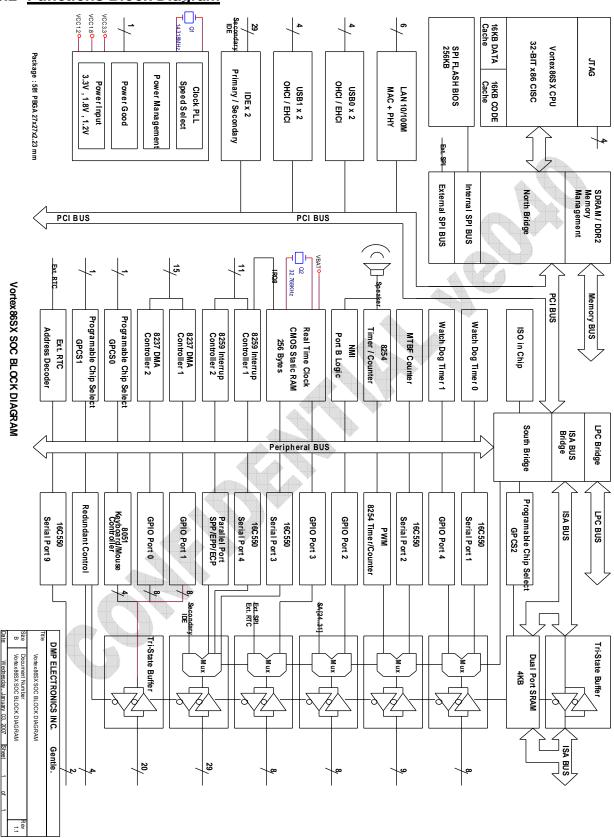

# 3 Block Diagram

## 3.1 System Block Diagram

# 3.2 Functions Block Diagram

# 3.3 PCI Device List

| Device#    | 0    | 1 | 2 | 3 | 4 | 5 | 6 | 7    | 8    | 9 | 10        | 11        | 12   | 13 |  |

|------------|------|---|---|---|---|---|---|------|------|---|-----------|-----------|------|----|--|

| IDSEL      | AD11 |   |   |   |   |   |   | AD18 | AD19 |   | AD21      | AD22      | AD23 |    |  |

| Function 0 | NB   |   |   |   |   |   |   | SB   | MAC  |   | USB0 OHCI | USB1 OHCI | IDE  |    |  |

| Function 1 |      |   |   |   |   |   |   |      |      |   | USB0 EHCI | USB1 EHCI |      |    |  |

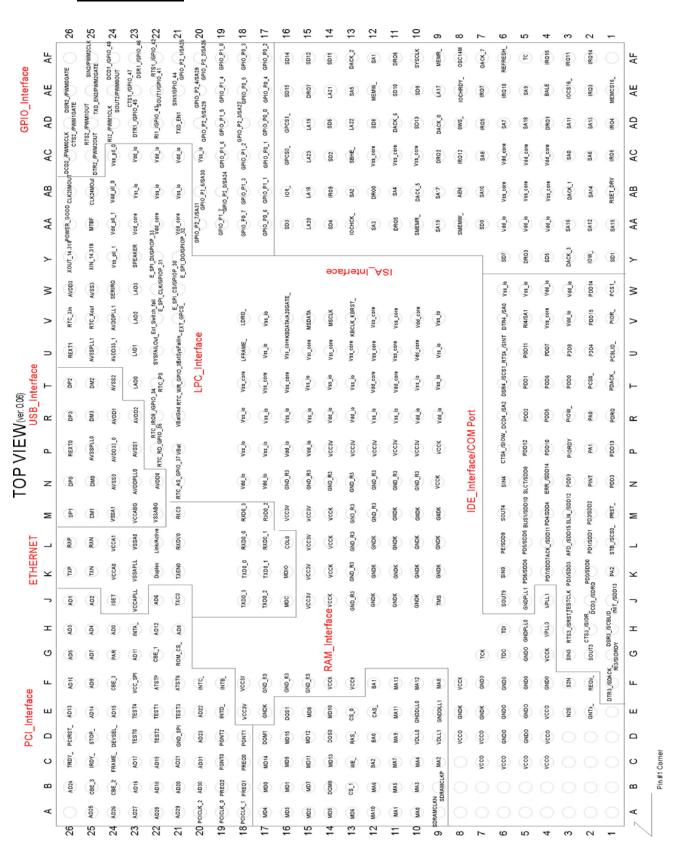

## 4 PIN Function List

### 4.1 BGA Ball Map

# 4.2 PINout Table

| A1 NCC F17 GND R3 P2 PA1 AA14 SD4 A2 NC F18 VCC3V P3 PIORDY AA15 LA20 A3 NC F19 NTB P4 PID10 AA16 SD3 A4 NC F20 NTC P5 PDD12 AA17 GPIO P0 6 A5 NC F21 ATSTN P6 CTS4 /SIOW AA18 GPIO P0 7 A5 NC F22 ATSTP P9 VCCK AA18 GPIO P1 7 A7 NC F22 ATSTP P9 VCCK AA18 GPIO P1 7 A7 NC F22 ATSTP P9 VCCX AA28 GPIO P2 7/SA31 A8 NC F24 GBE 0 P11 VCC3V AA20 GPIO P2 7/SA31 A8 NC F24 GBE 0 P11 VCC3V AA21 Vdd_core A9 SDRAMCLKN F25 AD9 P12 VCC3V AA22 Vdd_core A10 MA0 F26 AD10 P13 VCC3V AA22 Vdd_core A11 MA1 G1 RIJSIORDY P14 VCC3V AA22 Vdd_core A12 MA10 G2 SOUT3 P15 Vdd_io AA26 MTBF A13 MD6 G3 SIN3 P16 Vdd_io AA26 MTBF A14 MD5 G4 VCCK P17 VSs_io AB1 RSET_DRV A15 MD2 G5 GNDO P18 VSs_io AB2 SA14 A16 MD3 G6 TDO P21 VSs1 AB3 DACK 1 A17 MD4 G7 TCK P22 RTC RD GPIO 36 AB4 VSs_core A18 PCICLK 1 G21 ROM_CS P23 ANSS1 AB5 VSs_core A20 PCICLK 2 G23 AD11 P25 AVSSPLLO AB7 SA10 A21 AD29 G24 PAR P24 AVDD33 O AB8 AEN A22 AD28 G25 AD7 R1 PDRQ AB8 AFN A23 AD27 G26 AD5 R2 PA0 AB1 SA17 AD28 G25 AD7 R1 PDRQ AB8 AFN A23 AD27 G26 AD5 R2 PA0 AB1 SA17 AD4 G7 TCK B26 AD7 R1 PDRQ AB8 AFN A23 AD27 G26 AD5 R2 PA0 AB1 SA17 A24 AD26 H1 DSR3/SGBLID R3 PIOW AB1 SA4 A5 NC H2 P10 RA18 PIOW AB1 SA4 AD28 G25 AD7 R1 PDRQ AB8 AFN A23 AD27 G26 AD5 R2 PA0 AB10 DACK 5 A24 AD26 H1 DSR3/SGBLID R3 PIOW AB1 SA4 A25 AD28 G25 AD7 R1 PDRQ AB8 AFN A25 AD28 G25 AD7 R1 PDRQ AB8 AFN A26 NC H3 RTS3/SRST R5 PDD5 AB1 SA2 B1 NC H4 VPLLO R6 DCD4/SA2 AB1 RC9 B4 NC H2 AD8 R11 VSs_io AB1 SA4 B1 NC H4 VPLLO R6 DCD4/SA2 AB1 RC9 B4 NC H21 AD8 R11 VSs_io AB1 SA4 B1 NC H2 AD8 R11 VSs_io AB1 SA4 B1 NC H2 AD8 R11 NTA R13 Vdd io AB20 GPIO P2 G/SA30 B1 NC H22 AD12 R12 R12 VSs_io AB21 VSs_io B1 NC H22 AD12 R12 R12 VSs_io AB22 VSs_io B1 NC H22 AD12 R12 R12 VSs_io AB22 VSs_io B1 NC H22 AD12 R12 R12 VSs_io AB22 VSs_io B1 NC H22 AD0 R14 Vdd io AB20 GPIO P2 G/SA30 B1 NC H22 AD0 R14 Vdd io AB20 GPIO P2 G/SA30 B1 NA3 J1 NTT R18 R13 Vdd io AB20 GPIO P2 G/SA30 B1 NA5 J2 DCD3/SDRQ R18 VSs_io AB22 | Ball<br>No. | Function  | Ball<br>No. | Function     | Ball<br>No. | Function       | Ball<br>No. | Function       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|-------------|--------------|-------------|----------------|-------------|----------------|

| A3 NC F19 NTB P4 PDD10 AA16 SD3  A4 NC F20 NTC P5 PDD12 AA17 GPIO_P0_6  A5 NC F21 ATSTN P6 CTS4_/SIOW AA18 GPIO_P0_7  A6 NC F22 ATSTP P9 VCCK AA19 GPIO_P0_7  A7 NC F22 VCC_SPI P10 VCC3V AA20 GPIO_P2_7/SA31  A8 NC F24 CBE_0 P11 VCC3V AA21 Vdd_core  A8 NC F25 AD9 P12 VCC3V AA21 Vdd_core  A10 MA0 F26 AD10 P13 VCC3V AA21 Vdd_core  A11 MA1 G1 RIJSSIORDY P14 VCC3V AA22 Vdd_core  A11 MA1 G1 RIJSSIORDY P14 VCC3V AA22 Vdd_core  A12 MA10 G2 SOUT3 P15 Vdd_io A226 MTBF  A13 MD6 G3 SIN3 P16 Vdd_io A226 POWER GOOD  A14 MD5 G4 VCCK P17 VSs_io A81 RSET_DRV  A15 MD2 G5 GNDO P18 Vss_io A81 RSET_DRV  A16 MD3 G6 TDO P21 VBat A83 DACK_1  A17 MD4 G7 TCK P22 RTC_RD_GPIO_36 A84 Vss_core  A18 PCICK_1 G21 ROM_CS_ P23 AVSS1 AB5 Vss_core  A29 PCICK_2 G23 AD11 P25 AVSSPLLO AB7 SA10  A21 M22 G2 GE1 P26 REXTO A86 AEN  A22 AD28 G24 PAR P24 AVDD3_0 A88 AEN  A22 AD28 G25 AD5 RT P16 PA0 AB1 SA17  A23 AD27 G26 AD5 RT P24 AVDD3_0 A88 AEN  A24 AD29 G26 AD5 RT P24 AVDD3_0 A88 AEN  A25 AD27 G26 AD5 RT P26 AD5 AB1 SA27  A26 NC H3 RTSS_SCBLID R3 PIOW A811 SA4  ACC RD P17 VSs_io A81 SA10  A27 AD29 G26 AD5 R2 P24 AVDD3_0 A88 AEN  A28 AD27 G26 AD5 R2 P24 AVDD3_0 A88 AEN  A29 AD26 H1 DSR3_/SCBLID R3 PIOW A811 SA4  AD27 G26 AD5 R2 P24 AVDD3_0 A88 AEN  A21 AD29 G26 AD5 R2 P24 AVDD3_0 A88 AEN  A22 AD28 G25 AD7 R1 PDRQ A89 SA17  A23 AD27 G26 AD5 R2 PA0 A810 DACK_5  A24 AD26 H1 DSR3_/SCBLID R3 PIOW A811 SA4  AD27 G26 AD5 R2 PA0 A810 DACK_5  A25 AD25 H2 CTS_3_/SCBLID R3 PIOW A811 SA2  AD27 G26 AD5 R2 PA0 A810 DACK_5  A26 NC H3 RTS3_/SRST_ R5 PDD2 A818 SA2  AD28 G26 AD5 R2 PA0 A810 DACK_5  A27 AD28 G26 AD5 R2 PA0 A810 DACK_5  A28 AD27 G26 AD5 R2 PA0 A810 DACK_5  A29 AD26 H2 DSR3_/SCBLID R3 PIOW A811 SA4  AD29 G26 AD5 R3 R36 CDD2 A818 SA2  AD27 G26 AD5 R3 R36 CDD2 A818 SA2  AD28 G26 AD5 R3 R36 CDD2 A818 SA2  AD29 AD28 G26 AD5 R3 R36 CDD2 A818 SA2  AD29 AD28 G26 AD5 R3 R36 CDD2 A818 SA2  AD29 AD28 G26 AD5 R3 R36 CDD2 A818 SA2  AD29 AD28 G26 AD5 R3 R36 CDD2 A818 SA2  AD29 AD28 G26 AD5 R3 R36 CDD2 A818 SA17  A33 AD27 G26 AD5 A818 CDD2 A818 SA17  A34 AD29 AB4 AB4 AB4  | A1          | NC        | F17         | GND_R3       | P2          | PA1            | AA14        | SD4            |

| A4         NC         F20         NTC         P5         PDD12         AA17         GPIO_P0_6           A5         NC         F21         ATSTN         P6         CTS4_/SIOW         AA18_GPIO_P0_7           A6         NC         F22         ATSTP         P9         VCCK         AA19_GPIO_P1_7           A7         NC         F23         VCC_SPI         P10_VCG3V         AA20_GPIO_P2_7/SA31           A8         NC         F24         CBE_0         P11         VCC3V         AA21_Vdd_core           A9         SDRAMCLKN         F25         AA9         P12_VCC3V         AA22_Vdd_core           A11         MA10         M0         F26         AD10         P13_VCC3V         AA24_Vdd_pl_1           A11         MA10         G2         SOUT3         P15_Vdd_jo         AA26_FMTEP           A12         MA10         G2         SOUT3         P15_Vdd_jo         AA26_FWER_GOOD           A13         MD6         G3         SNN3         P16_Vdd_jo         AA26_FWER_GOOD           A14         MD5         G4_VCCK         P17_Vss_lo         AB1_RSET_DRV           A15         MD5         G4_VCCK         P17_Vss_lo         AB2_SA14           A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A2          | NC        | F18         | VCC3V        | P3          | PIORDY         | AA15        | LA20           |

| A5         NC         F21         ATSTN         P6         CTS4 /SIOW         AA18 GPIO P0 7           A6         NC         F22         ATSTP         P9         VCC X         AA19 GPIO P1 7           A7         NC         F23         VCC SPI         P10         VCC3V         AA20 GPIO P2 7/SA31           A8         NC         F24         CBE_0         P11         VCC3V         AA21 Vdd_core           A9         SDRAMCLKN         F25         AD9         P12         VCC3V         AA22 Vdd_core           A10         MA0         F26         AD10         P13         VCC3V         AA24 Vdd_pil_1           A11         MA11         G1         R13/SIORDY         P14         VCC3V         AA24 Vdd_pil_1           A12         MA10         G2         SOUT3         P15         Vdd_lo         AA26 POWER GOOD           A14         MD5         G4         VCCK         P17         Vss_lo         AB4         RSET_DRV           A15         MD2         G5         GNDO         P18         Vss_lo         AB4         Vss_COPE           A16         MD3         G6         TDO         P21         Wat         AB4         Vss_COPE <t< td=""><td>А3</td><td>NC</td><td>F19</td><td>INTB_</td><td>P4</td><td>PDD10</td><td>AA16</td><td>SD3</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А3          | NC        | F19         | INTB_        | P4          | PDD10          | AA16        | SD3            |

| A6         NC         F22         ATSTP         P9         VCCK         AA19         GPIO_P1_7           A7         NC         F23         VCC_SPI         P10         VCC3V         AA20         GPIO_P2_7/SA31           A8         NC         F24         CBE_0         P11         VCC3V         AA21         Vdd_core           A9         SDRAMCLKN         F25         AD9         P12         VCC3V         AA22         Vdd_core           A10         MA0         F26         AD10         P13         VCC3V         AA24         Vdd_core           A11         MA1         G1         Ri3/SIORDY         P14         VCC3V         AA24         Vdd_pll_1           A12         MA10         G2         SOUT3         P15         Vdd_lo         AA25         MTBF           A13         MD6         G3         SIN3         P16         Vdd_lo         AA26         POWER_GOOD           A14         MD5         G4         VCCK         P17         Vss_lo         AB1         RSET_DRV           A15         MD2         G5         GNDO         P18         Vss_lo         AB1         RSET_DRV           A15         MD2         G5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A4          | NC        | F20         | INTC_        | P5          | PDD12          | AA17        | GPIO_P0_6      |

| A7         NC         F23         VCC_SPI         P10         VCC3V         AA20 GPIO_P2_7/SA31           A8         NC         F24         CBE_0         P11         VCC3V         AA21 Vdd_core           A9         SDRAMCLKN         F25         AD9         P12         VCC3V         AA22 Vdd_core           A10         MA0         F26         AD10         P13         VCC3V         AA23 Vdd_core           A11         MA1         G1         RI3/SIORDY         P14         VCC3V         AA24 Vdd_pll_1           A12         MA10         G2         SOUT3         P15         Vdd_io         AA26 POWER_GOOD           A13         MD6         G3         SIN3         P16         Vdd_io         AA26 POWER_GOOD           A14         MD5         G4         VCCK         P17         Vs_io         AB1         RSET_DRV           A15         MD2         G5         GNDO         P18         Vs_io         AB1         RSET_DRV           A16         MD3         G6         TCK         P17         VS_io         AB2         SA14           A17         MD4         G7         TCK         P22         RTC_RO_PIO_36         AB4         Vs_s core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A5          | NC        | F21         | ATSTN        | P6          | CTS4_/SIOW_    | AA18        | GPIO_P0_7      |

| A8         NC         F24         CBE_0         P11         VCC3V         AA21         Vdc_core           A9         SDRAMCLKN         F25         AD9         P12         VCC3V         AA22         Vdd_core           A10         MA0         F26         AD10         P13         VCC3V         AA23         Vdd_core           A11         MA1         G1         RIS/SIORDY         P14         VCC3V         AA25         MTBF           A12         MA10         G2         SOUT3         P15         Vdd_io         AA25         MTBF           A13         MD6         G3         SIN3         P16         Vdd_io         AA26         POWER_GOOD           A14         MD5         G4         VCCK         P17         Vss_io         AB1         RSET_DRV           A15         MD2         G5         GNDO         P18         Vss_io         AB2         SA14           A16         MD3         G6         TDO         P21         VBat         AB3         DACK_1           A17         MD4         G7         TCK         P22         RTC_RD_GPIO_36         AB4         Vss_core           A18         PCICLK_1         G21         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A6          | NC        | F22         | ATSTP        | P9          | VCCK           | AA19        | GPIO_P1_7      |

| A9         SDRAMCLKN         F25         AD9         P12         VCC3V         AA22         Vdd_core           A10         MAO         F26         AD10         P13         VCC3V         AA23         Vdd_core           A11         MA1         G1         Ri3/SIORDY         P14         VCC3V         AA24         Vd_pll_1           A12         MA10         G2         SOUT3         P15         Vdd_io         AA25         MTBF           A12         MA10         G2         SOUT3         P15         Vdd_io         AA26         MTBF           A13         MD6         G3         SIN3         P16         Vdd_io         AA26         POWER_GOOD           A14         MD5         G4         VCCK         P17         Vss_io         AB1         RSET_DRV           A15         MD6         G4         VCCK         P17         Vss_io         AB1         RSET_DRV           A16         MD3         G6         TDO         P21         VBat         A83         DACK_1           A16         MD3         G6         TDO         P21         VBat         A84         Vss_core           A17         MD4         G7         TCK <td>A7</td> <td>NC</td> <td>F23</td> <td>VCC_SPI</td> <td>P10</td> <td>VCC3V</td> <td>AA20</td> <td>GPIO_P2_7/SA31</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A7          | NC        | F23         | VCC_SPI      | P10         | VCC3V          | AA20        | GPIO_P2_7/SA31 |

| A10 MA0 F26 AD10 P13 VCC3V AA23 Vdd_core A11 MA1 G1 RI3/SIORDY P14 VCC3V AA24 Vdd_pll_1 A12 MA10 G2 SOUT3 P15 Vdd_lo AA25 MTBF A13 MD6 G3 SIN3 P16 Vdd_lo AA26 POWER_GOOD A14 MD5 G4 VCCK P17 Vss_lo AB1 RSET_DRV A15 MD2 G5 GNDO P18 Vss_lo AB2 SA14 A16 MD3 G6 TDO P21 VS8t AB3 DACK_1 A17 MD4 G7 TCK P22 RTC_RD_GPIO_36 AB4 Vss_core A18 PCICLK_1 G21 ROM_CS P23 AVSS1 AB5 Vss_core A19 PCICLK_0 G22 CBE_1 P26 REXTO AB6 Vss_core A20 PCICLK_2 G23 AD11 P25 AVSSPLLO AB7 SA10 A21 AD29 G24 PAR P24 AVDD33_0 AB8 AEN A22 AD28 G25 AD7 R1 PDRQ AB9 SA17 A23 AD27 G26 AD5 R2 PA0 AB10 DACK_5 A24 AD26 H1 DSR3_SCBLID_R3 PIOW_AB11 SA4 A25 AD25 H2 CTS3_SIOR_R4 PDD5 AB12 DRQ0 A26 NC H3 RTS3_/SRST_R5 PDD2 AB13 SA2 B1 NC H6 TDI R10 Vdd_io AB16 IOR A27 AD8 NC H21 AD8 R11 Vss_io AB16 IOR B4 NC H21 AD8 R11 Vss_io AB16 IOR B4 NC H21 AD8 R11 Vss_io AB16 IOR B5 NC H22 AD12 R12 Vss_io AB16 IOR B6 NC H23 INTA_R1 ND AB6 IOR B7 NC H22 AD0 R14 Vss_io AB16 IOR B8 NC H23 INTA_R1 ND AB2 IOR B9 SDRAMCKP H26 AD3 R18 Vss_io AB18 GPIO_P1_3 B8 NC H23 INTA_R1 ND AB2 IOR B9 SDRAMCKP H26 AD3 R18 Vss_io AB21 Vss_io B9 SDRAMCKP H26 AD3 R18 VSs_io AB21 Vss_io B10 MA3 J1 INT_SDD13 R17 Vss_io AB21 Vss_io AB21 Vss_io B11 MA5 J2 DCD3_SDRQ R18 Vss_io AB22 Vss_io B12 MA6 J3 TESTCLK R21 Vss_io AB22 Vss_io B13 CS_1 J4 VPLL1 R22 R7C_IROS_GPIO_34 AB26 CLX25MOUT B14 DQM0 J5 GNDPLL1 R22 RYDS_AVD2 AC1 IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A8          | NC        | F24         | CBE_0        | P11         | VCC3V          | AA21        | Vdd_core       |

| A11         MA1         G1         Ri3/SIORDY         P14         VCC3V         AA24         Vdd_pll_1           A12         MA10         G2         SOUT3         P15         Vdd_io         AA26 MTBF           A13         MD6         G3         SIN3         P16         Vdd_io         AA26 POWER_GOOD           A14         MD5         G4         VCCK         P17         Vss_io         AB1         RSET_DRV           A15         MD2         G5         GNDO         P18         Vss_io         AB2         SA14           A16         MD3         G6         TDO         P21         VBat         AB3         DACK_1           A17         MD4         G7         TCK         P22         RTC_RD_GPIO_36         AB4         Vss_core           A18         PCICLK_1         G21         ROM_CS         P23         AVSS1         AB5         Vss_core           A18         PCICLK_1         G21         ROM_CS         P23         AVSS1         AB6         Vss_core           A19         PCICLK_2         G23         AD11         P25         AVSSPLLO         AB7         SA10           A22         AD28         G24         PAR         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A9          | SDRAMCLKN | F25         | AD9          | P12         | VCC3V          | AA22        | Vdd_core       |

| A12 MA10 G2 SOUT3 P15 Vdd_io AA25 MTBF A13 MD6 G3 SIN3 P16 Vdd_io AA26 POWER_GOOD A14 MD5 G4 VCCK P17 Vss_io AB1 RSET_DRV A15 MD2 G5 GNDO P18 Vss_io AB2 SA14 A16 MD3 G6 TDO P21 VBat AB3 DACK_1 A17 MD4 G7 TCK P22 RTC_RD_GPIO_36 AB4 Vss_core A18 PCICLK_1 G21 ROM_CS P23 AVSS1 AB5 Vss_core A19 PCICLK_0 G22 CBE_1 P26 REXTO AB6 Vss_core A20 PCICLK_2 G23 AD11 P25 AVSSPLLO AB7 SA10 A21 AD29 G24 PAR P24 AVDD33_0 AB8 AEN A22 AD28 G25 AD7 R1 PDRQ AB9 SA17 A23 AD27 G26 AD5 R2 PA0 AB10 DACK_5 A24 AD26 H1 DSR3_/SCBLID R3 PIOW_AB11 SA4 A25 AD25 H2 CTS3_/SIOR_R4 PDD5 AB12 DROO A26 NC H3 RTS3_/SRST_R5 PDD2 AB13 SA2 B1 NC H4 VPLO R6 DCD4_/SA2 AB14 IRQ9 B2 NC H5 GNDPLLO R9 Vdd_io AB15 LA18 B3 NC H6 TDI R10 Vdd_io AB16 IOR_ B4 NC H21 AD8 R11 Vss_io AB18 GPIO_P1_1 B5 NC H22 AD0 R14 Vss_io AB2 Vss_io AB2 Vss_io B9 SDRAMCLKP H26 AD3 R17 SDD1 AB2 Vss_io AB2 Vss_io B9 SDRAMCLKP H26 AD3 R17 Vss_io AB2 Vss_io AB2 Vss_io B1 MA3 J1 INIT_/SDD13 R17 Vss_io AB2 Vss_io AB2 CLK25MOUT B14 DQM0 J5 GNDPLL1 R22 AVDD2 AC1 IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A10         | MAO       | F26         | AD10         | P13         | VCC3V          | AA23        | Vdd_core       |

| A13 MD6 G3 SIN3 P16 Vdd_io AA26 POWER_GOOD A14 MD5 G4 VCCK P17 Vss_io AB1 RSET_DRV A15 MD2 G5 GNDO P18 Vss_io AB2 SA14 A16 MD3 G6 TDO P21 VSat AB3 DACK_1 A17 MD4 G7 TCK P22 RTC_RD_GPIO_36 AB4 Vss_core A18 PCICLK_1 G21 ROM_CS P23 AVSS1 AB6 Vss_core A19 PCICLK_0 G22 CBE_1 P26 REXTO AB6 Vss_core A20 PCICLK_2 G23 AD11 P25 AVSSPLLO AB7 SA10 A21 AD29 G24 PAR P24 AVDD33_0 AB8 AEN A22 AD28 G25 AD7 R1 PDRQ AB9 SA17 A23 AD27 G26 AD5 R2 PA0 AB10 DACK_5 A24 AD26 H11 DSR3_/SCBLID_R3 PIOW_AB11 SA4 A25 AD25 H2 CTS3_/SIOR_R4 PDD5 AB12 DRQ0 A26 NC H3 RTS3_/SRST_R5 PDD2 AB13 SA2 B1 NC H4 VPLLO R6 DCD4_/SA2 AB14 IRQ9 B2 NC H5 GNDPLLO R9 Vdd_io AB16 IOR_ B4 NC H21 AD8 R11 Vss_io AB16 IOR_ B4 NC H22 AD12 R12 Vss_io AB16 IOR_ B4 NC H23 INTA_R13 Vdd_io AB16 IOR_ B4 NC H24 AD0 R14 Vdd_io AB19 GPIO_P1_3 B6 NC H25 AD3 R14 Vss_io AB20 Vss_io B9 SDRAMCLKP H26 AD3 R17 VSs_io AB20 Vss_io B10 MA3 J1 INIT_/SDD13 R17 Vss_io AB20 Vss_io B11 MA5 J2 DCD3_/SDRQ R18 Vss_io AB22 Vss_io B12 MA5 J3 DCD3_/SDRQ R18 Vss_io AB22 Vss_io B13 NG H26 AD3 R15 Vss_io AB22 Vss_io B14 NA5 J2 DCD3_/SDRQ R18 Vss_io AB22 Vss_io B15 MA5 J2 DCD3_/SDRQ R18 Vss_io AB22 Vss_io B16 MA3 J1 INIT_/SDD13 R17 Vss_io AB22 Vss_io B17 MA5 J3 TESTCLK R21 V9B1GM AB26 CLK25MOUT B18 DQM0 J5 GNDPLL1 R23 AVDD2 AC1 IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A11         | MA1       | G1          | RI3/SIORDY   | P14         | VCC3V          | AA24        | Vdd_pll_1      |

| A14 MD5 G4 VCCK P17 VSS io AB1 RSET_DRV A15 MD2 G5 GNDO P18 VSS io AB2 SA14 A16 MD3 G6 TDO P21 VBat AB3 DACK_1 A17 MD4 G7 TCK P22 RTC_RD_GPIO_36 AB4 VSS_core A18 PCICLK_1 G21 ROM_CS_P23 AVSS1 AB5 VSS_core A19 PCICLK_0 G22 CBE_1 P26 REXTO AB6 VSS_core A20 PCICLK_2 G23 AD11 P25 AVSSPLLO AB7 SA10 A21 AD29 G24 PAR P24 AVDD33_0 AB8 AEN A22 AD28 G25 AD7 R1 PDRQ AB9 SA17 A23 AD27 G26 AD5 R2 PAO AB10 DACK_5 A24 AD26 H1 DSR3_/SCBLID R3 PIOW_AB11 SA4 A25 AD25 H2 CTS3_/SIOR_R4 PDD5 AB12 DRQ0 A26 NC H3 RTS3_/SRST_R5 PDD2 AB13 SA2 B1 NC H6 TDI R10 Vdd_io AB16 IOR_ B3 NC H6 TDI R10 Vdd_io AB16 GPIO_P1_1 B5 NC H24 AD0 R14 Vdd_io AB16 GPIO_P1_3 B6 NC H23 INTA_R13 Vdd_io AB16 GPIO_P1_3 B6 NC H23 INTA_R13 Vdd_io AB16 GPIO_P2_0/SA24 B7 NC H24 AD0 R14 Vdd_io AB16 GPIO_P1_3 B6 NC H23 INTA_R13 Vdd_io AB20 GPIO_P2_6/SA30 B8 NC H25 AD4 R15 VSS_io AB21 VSS_io B9 SDRAMCLKP H26 AD3 R17 VSS_io AB22 VSS_io B10 MA3 J1 INIT_/SDD13 R17 VSS_io AB22 VSS_io B11 MA5 J2 DCD3_/SDRQ R18 VSS_io AB26 CLK25MOUT B14 DQM0 J5 GNDPLL1 R22 RTC_IRQ8_/GPIO_34 AB26 CLK25MOUT B14 DQM0 J5 GNDPLL1 R22 RTC_IRQ8_/GPIO_34 AB26 CLK25MOUT B14 DQM0 J5 GNDPLL1 R22 RTC_IRQ8_/GPIO_34 AB26 CLK25MOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A12         | MA10      | G2          | SOUT3        | P15         | Vdd_io         | AA25        | MTBF           |

| A15 MD2 G5 GNDO P18 Vss io AB2 SA14  A16 MD3 G6 TDO P21 VBat AB3 DACK_1  A17 MD4 G7 TCK P22 RTC_RD_GPIO_36 AB4 Vss_core  A18 PCICLK_1 G21 ROM_CS P23 AVSS1 AB5 Vss_core  A19 PCICLK_0 G22 CBE_1 P26 REXTO AB6 Vss_core  A20 PCICLK_2 G23 AD11 P25 AVSSPLLO AB7 SA10  A21 AD29 G24 PAR P24 AVDD33_0 AB8 AEN  A22 AD28 G25 AD7 R1 PDRQ AB9 SA17  A23 AD27 G26 AD5 R2 PA0 AB10 DACK_5  A24 AD26 H1 DSR3_/SCBLID R3 PIOW_ AB11 SA4  A25 AD25 H2 CTS3_/SIOR_ R4 PDD5 AB12 DRQO  A26 NC H3 RTS3_/SRST_ R5 PDD2 AB13 SA2  B1 NC H4 VPLLO R6 DCD4_/SA2 AB14 IRQ9  B2 NC H5 GNDPLLO R9 Vdd_io AB16 [OR_ B4 NC H21 AD8 R11 Vss_io AB16 [OR_ B4 NC H22 AD12 R12 Vss_io AB16 GPIO_P1_1  B5 NC H22 AD12 R12 Vss_io AB19 GPIO_P1_3  B6 NC H23 INTA R13 Vdd_io AB20 GPIO_P2_G/SA30  B8 NC H26 AD3 R16 Vss_io AB21 Vss_io  B9 SDRAMCLKP H26 AD3 R18 Vss_io AB21 Vss_io  B9 SDRAMCLKP H26 AD3 R16 Vss_io AB22 Vss_io  B10 MA3 J1 INIT_/SDD13 R17 Vss_io AB22 Vss_io  B11 MA6 J3 TESTCLK R21 VSs_io AB22 Vss_io  B12 MA6 J3 TESTCLK R21 VSs_io AB22 CLK25MOUT  B14 DQM0 J5 GNDPLL1 R22 AVD2 AC1 IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A13         | MD6       | G3          | SIN3         | P16         | Vdd_io         | AA26        | POWER_GOOD     |

| A16         MD3         G6         TDO         P21         VBat         AB3         DACK_1           A17         MD4         G7         TCK         P22         RTC_RD_GPIO_36         AB4         Vss_core           A18         PCICLK_1         G21         ROM_CS         P23         AVSS1         AB5         Vss_core           A19         PCICLK_0         G22         CBE_1         P26         REXTO         AB6         Vss_core           A20         PCICLK_2         G23         AD11         P25         AVSSPLLO         AB6         Vss_core           A20         PCICLK_2         G23         AD11         P25         AVSSPLLO         AB6         Vss_core           A20         PCICLK_2         G23         AD11         P25         AVSSPLLO         AB6         Vss_core           A20         AD29         G24         PAR         P24         AVD033_0         AB8         AEN           A22         AD28         G25         AD7         R1         PPRQ         AB9         SA17           A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A14         | MD5       | G4          | VCCK         | P17         | Vss_io         | AB1         | RSET_DRV       |

| A17         MD4         G7         TCK         P22         RTC_RD_GPIO_36         AB4         Vss_core           A18         PCICLK_1         G21         ROM_CS         P23         AVSS1         AB5         Vss_core           A19         PCICLK_0         G22         CBE_1         P26         REXTO         AB6         Vss_core           A20         PCICLK_2         G23         AD11         P25         AVSSPLLO         AB7         SA10           A21         AD29         G24         PAR         P24         AVDD33_0         AB8         AEN           A22         AD28         G25         AD7         R1         PDRQ         AB9         SA17           A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1         DSR3_/SCBLID         R3         PIOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A15         | MD2       | G5          | GNDO         | P18         | Vss_io         | AB2         | SA14           |

| A18         PCICLK_1         G21         ROM_CS         P23         AVSS1         AB5         Vss_core           A19         PCICLK_0         G22         CBE_1         P26         REXT0         AB6         Vss_core           A20         PCICLK_2         G23         AD11         P25         AVSSPLL0         AB7         SA10           A21         AD29         G24         PAR         P24         AVD033_0         AB8         AEN           A22         AD28         G25         AD7         R1         PDRQ         AB9         SA17           A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1         DSR3_/SCBLID         R3         PIOW_         AB11         SA4           A25         AD25         H2         CTS3_/SIOR_         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14 IRQ9           B2         NC         H5         GNDPLL0 <t< td=""><td>A16</td><td>MD3</td><td>G6</td><td>TDO</td><td>P21</td><td>VBat</td><td>AB3</td><td>DACK 1</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A16         | MD3       | G6          | TDO          | P21         | VBat           | AB3         | DACK 1         |

| A18         PCICLK_1         G21         ROM_CS         P23         AVSS1         AB5         Vss_core           A19         PCICLK_0         G22         CBE_1         P26         REXT0         AB6         Vss_core           A20         PCICLK_2         G23         AD11         P25         AVSSPLL0         AB7         SA10           A21         AD29         G24         PAR         P24         AVDD33_0         AB8         AEN           A22         AD28         G25         AD7         R1         PDRQ         AB9         SA17           A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1         DSR3_/SCBLID         R3         PIOW         AB11         SA4           A25         AD25         H2         CTS3_/SIOR         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14  RQ9           B2         NC         H5         GNDPLL0         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A17         | MD4       | G7          | TCK          | P22         | RTC RD GPIO 36 | AB4         | Vss core       |

| A20         PCICLK_2         G23         AD11         P25         AVSSPLL0         AB7         SA10           A21         AD29         G24         PAR         P24         AVDD33_0         AB8         AEN           A22         AD28         G25         AD7         R1         PDRQ         AB9         SA17           A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1         DSR3_/SCBLID_         R3         PIOW_         AB11         SA4           A25         AD25         H2         CTS3_/SIOR_         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14         IRQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB15         LA18           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11 </td <td>A18</td> <td>PCICLK_1</td> <td>G21</td> <td>ROM_CS_</td> <td>P23</td> <td>AVSS1</td> <td>AB5</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A18         | PCICLK_1  | G21         | ROM_CS_      | P23         | AVSS1          | AB5         |                |

| A20         PCICLK_2         G23         AD11         P25         AVSSPLL0         AB7         SA10           A21         AD29         G24         PAR         P24         AVDD33_0         AB8         AEN           A22         AD28         G25         AD7         R1         PDRQ         AB9         SA17           A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1         DSR3_/SCBLID_         R3         PIOW_         AB11         SA4           A25         AD25         H2         CTS3_/SIOR_         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14         IRQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB15         LA18           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11 </td <td>A19</td> <td>PCICLK_0</td> <td>G22</td> <td>CBE_1</td> <td>P26</td> <td>REXT0</td> <td>AB6</td> <td>Vss_core</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A19         | PCICLK_0  | G22         | CBE_1        | P26         | REXT0          | AB6         | Vss_core       |

| A22         AD28         G25         AD7         R1         PDRQ         AB9         SA17           A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1         DSR3_/SCBLID_         R3         PIOW_         AB11         SA4           A25         AD25         H2         CTS3_/SIOR_         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14         IRQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB16         ICR_           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P2_6/SA20           B6         NC         H23         INTA_ <td< td=""><td></td><td></td><td>G23</td><td>AD11</td><td>P25</td><td>AVSSPLL0</td><td>AB7</td><td>SA10</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |           | G23         | AD11         | P25         | AVSSPLL0       | AB7         | SA10           |

| A23         AD27         G26         AD5         R2         PA0         AB10         DACK_5           A24         AD26         H1         DSR3_/SCBLID_         R3         PIOW_         AB11         SA4           A25         AD25         H2         CTS3_/SIOR_         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14         IRQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB16         ICR_           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_1           B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P2_6/SA30           B7         NC         H24         AD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A21         | AD29      | G24         | PAR          | P24         | AVDD33 0       | AB8         | AEN            |

| A24         AD26         H1         DSR3_/SCBLID_         R3         PIOW_         AB11         SA4           A25         AD25         H2         CTS3_/SIOR_         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14         IRQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB15         LA18           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_3           B6         NC         H23         INTA_         R13         Vdd_io         AB18         GPIO_P2_0/SA24           B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4 </td <td>A22</td> <td>AD28</td> <td>G25</td> <td>AD7</td> <td>R1</td> <td>PDRQ</td> <td>AB9</td> <td>SA17</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A22         | AD28      | G25         | AD7          | R1          | PDRQ           | AB9         | SA17           |

| A25         AD25         H2         CTS3_/SIOR_         R4         PDD5         AB12         DRQ0           A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14         IRQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB15         LA18           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_3           B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P2_0/SA24           B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3 </td <td>A23</td> <td>AD27</td> <td>G26</td> <td>AD5</td> <td>R2</td> <td>PA0</td> <td>AB10</td> <td>DACK_5</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A23         | AD27      | G26         | AD5          | R2          | PA0            | AB10        | DACK_5         |

| A26         NC         H3         RTS3_/SRST_         R5         PDD2         AB13         SA2           B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14         IRQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB15         LA18           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR           B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_3           B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P1_3           B6         NC         H24         AD0         R14         Vdd_io         AB19         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB20         GPIO_P2_6/SA30           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB21         Vss_io           B10         MA3         J1         INIT_/S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A24         | AD26      | H1          | DSR3 /SCBLID | R3          | PIOW           | AB11        | SA4            |

| B1         NC         H4         VPLL0         R6         DCD4_/SA2         AB14  RQ9           B2         NC         H5         GNDPLL0         R9         Vdd_io         AB15   LA18           B3         NC         H6         TDI         R10         Vdd_io         AB16   lOR_           B4         NC         H21         AD8         R11         Vss_io         AB17   GPIO_P1_1           B5         NC         H22   AD12         R12   Vss_io         AB18   GPIO_P1_3           B6         NC         H23   INTA_         R13   Vdd_io         AB19   GPIO_P2_0/SA24           B7         NC         H24   AD0         R14   Vdd_io         AB20   GPIO_P2_6/SA30           B8         NC         H25   AD4         R15   Vss_io         AB21   Vss_io           B9         SDRAMCLKP         H26   AD3         R16   Vss_io         AB22   Vss_io           B10         MA3         J1   INIT_/SDD13         R17   Vss_io         AB23   Vss_io           B11         MA5         J2   DCD3_/SDRQ         R18   Vss_io         AB24   Vdd_pll_0           B12         MA6         J3   TESTCLK         R21   VBatGnd         AB25   CLK24MOut           B14         DQM0         J5   GNDPLL1         R22   RTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A25         | AD25      | H2          | CTS3_/SIOR_  | R4          | PDD5           | AB12        | DRQ0           |

| B2         NC         H5         GNDPLLO         R9         Vdd_io         AB15         LA18           B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_3           B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P2_0/SA24           B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB22         Vss_io           B10         MA3         J1         INIT_/SDD13         R17         Vss_io         AB23         Vss_io           B11         MA5         J2         DCD3_/SDRQ         R18         Vss_io         AB24         Vdd_pll_0           B12         MA6         J3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A26         | NC        | НЗ          | RTS3_/SRST_  | R5          | PDD2           | AB13        | SA2            |

| B3         NC         H6         TDI         R10         Vdd_io         AB16         IOR_           B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_3           B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P2_0/SA24           B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB22         Vss_io           B10         MA3         J1         INIT_/SDD13         R17         Vss_io         AB23         Vss_io           B11         MA5         J2         DCD3_/SDRQ         R18         Vss_io         AB24         Vdd_pli_0           B12         MA6         J3         TESTCLK         R21         VBatGnd         AB25         CLK24MOut           B14         DQM0         J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | B1          | NC        | H4          |              | R6          | DCD4 /SA2      | AB14        | IRQ9           |

| B4         NC         H21         AD8         R11         Vss_io         AB17         GPIO_P1_1           B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_3           B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P2_0/SA24           B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB22         Vss_io           B10         MA3         J1         INIT_/SDD13         R17         Vss_io         AB23         Vss_io           B11         MA5         J2         DCD3_/SDRQ         R18         Vss_io         AB24         Vdd_pII_0           B12         MA6         J3         TESTCLK         R21         VBatGnd         AB25         CLK24MOut           B13         CS_1         J4         VPLL1         R22         RTC_IRQ8_/GPIO_34         AB26         CLK25MOUT           B14         DQM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B2          | NC        | H5          | GNDPLL0      | R9          | Vdd_io         | AB15        | LA18           |

| B5         NC         H22         AD12         R12         Vss_io         AB18         GPIO_P1_3           B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P2_0/SA24           B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB22         Vss_io           B10         MA3         J1         INIT_/SDD13         R17         Vss_io         AB23         Vss_io           B11         MA5         J2         DCD3_/SDRQ         R18         Vss_io         AB24         Vdd_pll_0           B12         MA6         J3         TESTCLK         R21         VBatGnd         AB25         CLK24MOut           B13         CS_1         J4         VPLL1         R22         RTC_IRQ8_/GPIO_34         AB26         CLK25MOUT           B14         DQM0         J5         GNDPLL1         R23         AVDD2         AC1         IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ВЗ          | NC        | H6          | TDI          | R10         | Vdd_io         | AB16        | IOR_           |

| B6         NC         H23         INTA_         R13         Vdd_io         AB19         GPIO_P2_0/SA24           B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB22         Vss_io           B10         MA3         J1         INIT_/SDD13         R17         Vss_io         AB23         Vss_io           B11         MA5         J2         DCD3_/SDRQ         R18         Vss_io         AB24         Vdd_pll_0           B12         MA6         J3         TESTCLK         R21         VBatGnd         AB25         CLK24MOut           B13         CS_1         J4         VPLL1         R22         RTC_IRQ8_/GPIO_34         AB26         CLK25MOUT           B14         DQM0         J5         GNDPLL1         R23         AVDD2         AC1         IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B4          | NC        | H21         | AD8          | R11         | Vss_io         | AB17        | GPIO_P1_1      |

| B7         NC         H24         AD0         R14         Vdd_io         AB20         GPIO_P2_6/SA30           B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB22         Vss_io           B10         MA3         J1         INIT_/SDD13         R17         Vss_io         AB23         Vss_io           B11         MA5         J2         DCD3_/SDRQ         R18         Vss_io         AB24         Vdd_pll_0           B12         MA6         J3         TESTCLK         R21         VBatGnd         AB25         CLK24MOut           B13         CS_1         J4         VPLL1         R22         RTC_IRQ8_/GPIO_34         AB26         CLK25MOUT           B14         DQM0         J5         GNDPLL1         R23         AVDD2         AC1         IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | B5          | NC        | H22         | AD12         | R12         | Vss_io         | AB18        | GPIO_P1_3      |

| B8         NC         H25         AD4         R15         Vss_io         AB21         Vss_io           B9         SDRAMCLKP         H26         AD3         R16         Vss_io         AB22         Vss_io           B10         MA3         J1         INIT_/SDD13         R17         Vss_io         AB23         Vss_io           B11         MA5         J2         DCD3_/SDRQ         R18         Vss_io         AB24         Vdd_pll_0           B12         MA6         J3         TESTCLK         R21         VBatGnd         AB25         CLK24MOut           B13         CS_1         J4         VPLL1         R22         RTC_IRQ8_/GPIO_34         AB26         CLK25MOUT           B14         DQM0         J5         GNDPLL1         R23         AVDD2         AC1         IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | В6          | NC        | H23         | INTA_        | R13         | Vdd_io         | AB19        | GPIO_P2_0/SA24 |